Hi Sir,

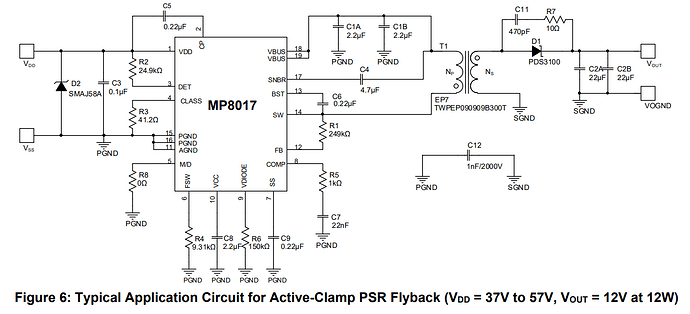

We have selected the MP8017 PD controller and designed a PoE-based power solution targeting a 12V output.

During testing, we applied power through a PoE injector and observed approximately 46V at the bridge rectifier input, which is within the expected range. We also provided an external VCC supply of 5.2V for proper startup.

However, we are currently observing an output voltage of around 17V under no-load conditions, whereas the design target is 12V.

We would like your support in understanding and resolving this issue. Specifically:

-

Is this behavior expected under no-load or light-load conditions?

-

Are there any recommended minimum load requirements for proper regulation?

-

Could you suggest any design improvements to achieve tighter output regulation?

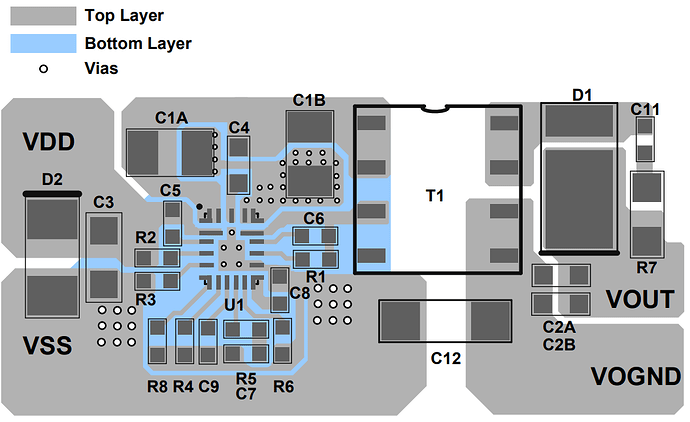

We have referred to the evaluation board design (EVL8017-L-00A) and request you to kindly share:

-

Detailed schematics (if available beyond the reference)

-

User guide / application notes for debugging

Due to tight project timelines, your prompt support would be highly appreciated.

Best regards,

Samudralankaia