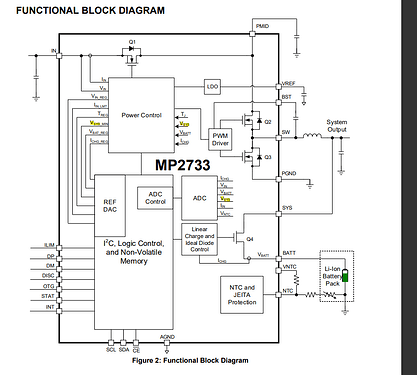

Hi, I have a general question about something I’m struggling to understand. For battery charging ICs with a NVDC Power Path (e.g. the MP2733), I see there’s something called Vsys_min, then - separately - there’s a lower Vbatt_uvlo threshold.

Most datsheets I read say something like “the system voltage is regulated at Vsys_min”. But, is this ONLY when an input power adaptor (e.g. a USB connector) is present? And, if no adaptor is present, Vsys ‘follows’ the voltage of the battery (plus some offset)?

I guess what I’m trying to wrap my head around is the case when Vbatt falls below Vsys_min when no adaptor is present. Does the IC boost the Vbatt up to Vsys_min? Or does it continue to use the battery down to Vbatt_uvlo?

I don’t see anything in these datasheets that suggest boost behavior, but I also notice that the wording about Vsys_min is a little confusing (at least to me, who is new to learning about charging ICs).

Thanks for any insight!