I am using an MPM54524 on a board where Buck A and B are setup in a parallel configuration (VSA+ and VSB+ are connected) and I would like to move from using AVP to interleaved mode for load balancing. I have custom software (that has been THOROUGHLY tested and successfully programmed hundreds of MPM54524s) that writes a configuration into the device and I am able to write every register in the configuration except for being able to write a value of 0x20 (bit 5 as ‘1’) to register 0x14 (PROTECT_REG) which enables A/B interleaved mode. When I write 0x20 to register 0x14 it just reads back as 0x00. Is there something specific I need to do to enable interleaved mode? Or some order I need to write registers in?

Hello @stephen.cline,

I wanted to clarify on the setting steps. Have you pulled down EN pin before writing 0x20 to the register 0x14? If not, please pull down EN pin and then write the value to the register.

Yes, I have the EN pin pulled down before writing the register. I tried this on my custom board with my custom software and also on the MPM54524 evaluation board using VBP4 and the MPS dongle, neither device will allow me to set a value of 0x20 to register 0x14 with the EN pin pulled down.

Hello @stephen.cline,

Once the EN pin is pulled down, write 0x20 to the 0x14 register and don’t read. Instead, write to ROM. Turn the input power off and then turn back on. Have you followed these steps in order?

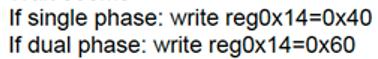

That worked, however is extremely confusing. What is the process to do this with custom software? Since register 0x14 needs to be written to store to MTP, how do you not undo the setting of bit 5 when setting bit 6 to disable MTP write protection?

Hello @stephen.cline,

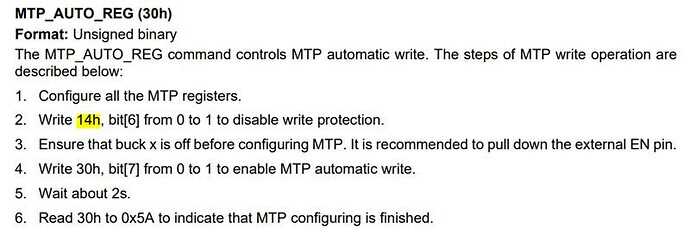

Please refer to the steps for configuring MTP_AUTO_REG register in the DS.

Please let me know if this helps.