Dear support member.

Please answer as soon as possible.

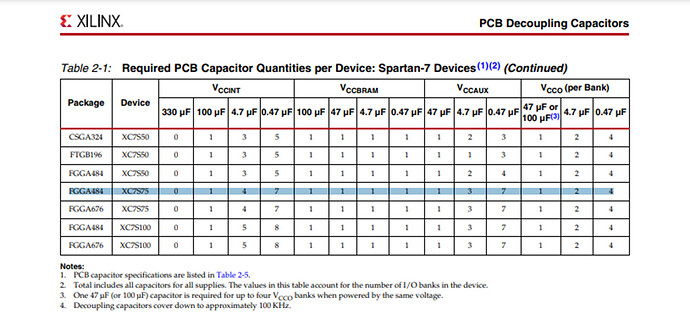

My customer use MPM3650C and MPM3632S for Spartan-7.

This FPGA requested many capacitance.

(refer to table.)

I’m worried about inrush current, but should I design it according to the required capacitors of table?

What should I do if the capacity listed in the table cannot be used?

Best regards.

Dear support member.

I’m sorry to hurry, but can you confirm it?

best regards.

Short answer… Defiantly YES…

FPGA’s are sensitive to issues on the PSU lines

But now for the details…

Have a look at this page…

https://ridleyengineering.com/images/phocadownload/1%20second%20stage%20filter%20design.pdf

This is about a 2 stage filter but you can also read it as isolating large capacitor loads from a buck converter.

There is also a seriously good app note on capacitor selection/placement by Xilinx.

I believe this has the trimmed down version… (I read and used the article 15 years ago!)

Things to remember… smallest value closest to the power pins, 10 uF or larger can be several cm from the FPGA. Ignore the OSCON and TANT and use high value ceramics.

Consider ferrite beads between supplies and the FPGA (again isolates the capacitance & keeps circulating currents small).

As far as inrush is concerned, SS pin controls inrush by limiting voltage change, just make sure you power supply sequencing is correct for the device, and be careful of negative going transitions during PSU rise.

Simon